# **A-Level Physics**

# **Digital Signal Processing**

**Mark Scheme**

Time available: 58 minutes Marks available: 44 marks

www.accesstuition.com

## Mark schemes

1.

(a) *Ā* **√**

. B **√**

Ā.B√

Do not allow  $\overline{A} + \overline{B}$

(b) EOR ✓

Accept: XOR; EXOR; Exclusive OR gate

1

2

(c)

| В | Α | C | D | E | X | Y | Z |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | 1 | 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 | 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 0 |

| 1 | 1 | 0 | 0 | 0 | 0 | 1 | 0 |

X and Z correct ✓

Y correct ✓

2

(d) NOR gate ✓

Also accept any of:

EXNOR; ENOR; XNOR; Exclusive NOR gate

Z

1

(e)

X Y

✓

A > B A = B A < B

1

[7]

- 2.

- (a) When  $V_{\rm c}$  reaches a value of  $V_{\rm u}$ , the output voltage  $V_{\rm out}$  drops LOW.  $\checkmark$

- The capacitor now discharges through the resistor causing the value of  $V_{\rm c}$  to fall.  $\checkmark$

- When  $V_{\rm c}$  reaches a value of  $V_{\rm L}$ , the output voltage  $V_{\rm out}$  jumps HIGH.  $\checkmark$

3

#### (b) Mark-to-space ratio

$R_{\rm B}$  gets smaller and hence ( $t_{\rm H}$ ) is reduced

OR

$R_{\mathsf{A}}$  gets bigger and hence  $(t_{\mathsf{L}})$  is increased  $\checkmark$

First mark: Either statement or equivalent labelled diagram(s).

Hence mark:space ratio is reduced / smaller ✓

Second mark: Conclusion

$$\Pr{\text{PRF} = \frac{1}{T} = \frac{1}{(t_H + t_L)} = \frac{1}{0.7C (2R + R_A + R_B)}}$$

The total resistance  $(2R + R_A + R_B)$  is constant  $\checkmark$

As a result of a constant resistance in the circuit, PRF does not change \( \strict{\sqrt{}} \)

First mark: explanation of how total resistance in the circuit affects

the periodic time

Second mark: Conclusion.

[7]

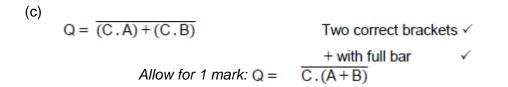

**3.** (a)

|   | Output |   |   |

|---|--------|---|---|

| С | В      | Α | Q |

| 0 | 0      | 0 | 0 |

| 0 | 0      | 1 | 0 |

| 0 | 1      | 0 | 0 |

| 0 | 1      | 1 | 0 |

| 1 | 0      | 0 | 1 |

| 1 | 0      | 1 | 0 |

| 1 | 1      | 0 | 1 |

| 1 | 1      | 1 | 1 |

All Q states correct for 1 mark

1

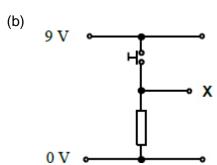

Correct orientation for resistor & switch  $\checkmark$

Correct tap-off point for X ✓

(d) The gate acts as an inverter  $\checkmark$

Accept 'NOT' as the function

(e) Must be a reason and a consequence for the mark. ✓

eg Uses only one type of logic gate so need to hold less stock OR

Uses only one chip rather than two so circuit board can be smaller / less power needed / cheaper

Do not allow: Less complex circuit

**4.** (a) Difference: BCD counter outputs binary codes. A Johnson decade counter outputs a single output sequentially**√**

Similarity: Both counters recycle at the 10<sup>th</sup> pulse ✓

Both outputs described.

Condone – max counter value for 10<sup>th</sup> pulse.

Accept: both counters count from 0-9

OR both counters count to 10

2

2

2

1

1

[7]

### (b) Duty cycle:

From oscilloscope  $t_{\rm on}$  = 3 div @ 50  $\mu \rm s$  / div = 150  $\mu \rm s$  OR

$$t_{\rm off}$$

= 2 div @ 50 µs / div = 100 µs  **$\checkmark$**

$$\frac{t_{\text{ou}}}{(t_{\text{ou}} + t_{\text{off}})} \times 100 = 60\% \qquad \text{OR} \quad 0.6 \quad \checkmark$$

(accept 'divisions' to signify the values of  $t_{on}$  and  $t_{off}$ )

Frequency:

From CRO  $t_p = 5 \text{ div } @ 50 \text{ } \mu\text{s} / \text{ div}$

$$t_{\rm p}$$

= 250 µs

$$f = 1/t_p = 4 \text{ kHz } \checkmark$$

Only 1 mark for:

either of  $t_{on}$  or  $t_{off}$  correct but duty cycle wrong

OR

correct use of both wrong  $t_{on}$  and  $t_{off}$

One mark for:

correct use of their  $t_{on} + t_{off}$

(c) **BCD**:  $Q_2 = 600 / 10 = 60 \text{ Hz } \checkmark$

(only one pulse is produced in 10 clock pulses at Q2)

**Johnson:**  $Q_2 = 600 / 10 = 60 \text{ Hz } \checkmark$

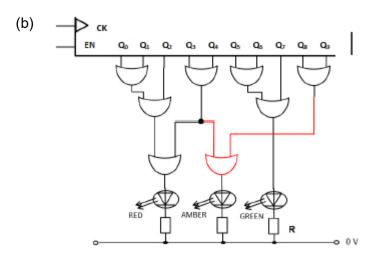

**5.** (a)

Flat line of  $Q_0$  - 1 mark

Correct fall of Q<sub>1</sub> and rise of Q<sub>2</sub> - 1 mark

2

3

2

[7]

Logic OR gate correctly connected in position for 1 mark

(c) The ON time for the green LED is determined by:

the frequency of the clock ✓

the number of adjacent outputs that are OR'ed ✓

Accept reference to the period of the clock pulse.

(d)  $\mathbf{R} = V_R / I$ ;  $\mathbf{R} = (9 - 2.1) V \checkmark / 9 \text{ mA}$

R = 6.9 V / 9 mA;  $R = 767 \Omega \checkmark$

Minimum resistor value that can be used in order not to exceed 9 mA is 767  $\Omega$ .

The 720  $\Omega$  resistor range is (684 to 756)  $\Omega$  and falls below this value so should not be used.  $\checkmark$

OR

Calculation using 720  $\Omega$  ±5% Resistor range = (684 to 756)  $\Omega$   $\checkmark$  leading to smallest current of 9.1 mA  $\checkmark$

This current will exceed the permitted value of 9 mA. Don't use. ✓

1 One mark for voltage across the resistor

2One mark for a suitable I-V-R calculation

3One mark for conclusion with reason.

Use of error range to give max resistance must be seen in either  $_2$  or  $_3$  for that mark to be awarded.

Г

3

1

2

[8]

6.

(a)

| A | В | а | b | С | d | е | f | g | Display |

|---|---|---|---|---|---|---|---|---|---------|

| 0 | 0 | 0 | 0 | 0 | 1 | 1 | 1 | 0 | L       |

| 0 | 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | S       |

| 1 | 0 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | S       |

| 1 | 1 | 0 | 1 | 1 | 0 | 1 | 1 | 1 | Н       |

1 mark for row L

1 mark for row S (both)

1 mark for row H

(b) EXOR gate

1

3

(c) (i) Different combinations produce different brightness 1 Disadvantage

1

(ii) R=V/I; (5V - 2.2V) / 20mA;  $2.8V / 20mA = 140\Omega$ 1 mark for 2.8V drop 1 mark for answer

2

(iii) E24 =  $150\Omega$

1 mark for answer

1

(8)