## **A-Level Physics**

## **Digital Signal Processing**

**Question Paper**

Time available: 58 minutes Marks available: 44 marks

www.accesstuition.com

1. The dia

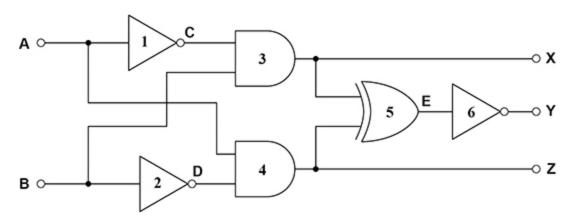

The diagram below shows a logic system made of logic gates labelled  ${\bf 1}$  to  ${\bf 6}$

The logic system has inputs A and B and outputs X, Y and Z.

(a) Write the simplest Boolean algebra expression for output **X** in terms of inputs **A** and **B**.

(b) State the name of logic gate 5 in the figure above.

| <br> | <br> |  |

|------|------|--|

|      |      |  |

|      |      |  |

|      |      |  |

(c) Complete the table below, the truth table for this logic system.

| В | A | C | D | Е | X | Y | Z |

|---|---|---|---|---|---|---|---|

| 0 | 0 | 1 | 1 | 0 |   |   |   |

| 0 | 1 | 0 | 1 | 1 |   |   |   |

| 1 | 0 | 1 | 0 | 1 |   |   |   |

| 1 | 1 | 0 | 0 | 0 |   |   |   |

(d) Suggest a single logic gate that can replace the combination of gates  ${\bf 5}$  and  ${\bf 6}$  in this system.

(1)

(2)

(1)

(e) The logic system in above diagram is designed to indicate which of inputs A and B has the larger binary value, or whether the values are the same. Each decision is indicated by one of the outputs X, Y or Z becoming a logic 1

Which row identifies the outputs X, Y and Z?

Tick (✓) one box.

(1) (Tatal 7 marks)

(Total 7 marks)

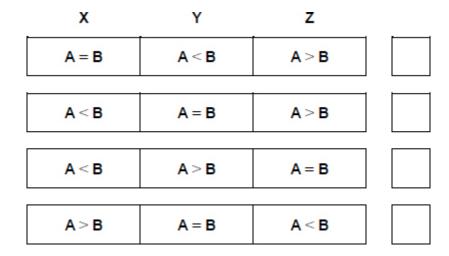

**2. Figure 1** shows a type of NOT gate called a Schmitt Trigger. This is connected to a capacitor of capacitance *C* and a resistor of resistance *R* to make an oscillator circuit. The circuit is used to produce continuous clock pulses.

Figure 1

$V_{\mathrm{out}}$  switches HIGH or LOW when the input voltage  $V_{\mathrm{c}}$  passes through one of two trigger voltage values.

The output voltage  $V_{\mathrm{out}}$  switches to:

- LOW when  $V_{

m c}$  rises and reaches the upper trigger voltage  $V_{

m U}$

- HIGH when  $V_{

m c}$  falls and reaches the lower trigger voltage  $V_{

m L}$ .

| Initially the capacitor is uncharged and $V_{\rm c}$ is at $0~{ m V}.$                                                                  |

|-----------------------------------------------------------------------------------------------------------------------------------------|

| Explain the sequence of actions of this circuit as the output goes through one full cycle. The first two stages have been done for you. |

| You should refer to the $RC$ circuit in <b>Figure 1</b> and to $V_{ m U}$ and $V_{ m L}$ in your answer.                                |

| <b>Stage 1</b> : Since $V_{ m c}$ is LOW, the output is HIGH.                                                                           |

| <b>Stage 2</b> : The capacitor now charges through the resistor, making $V_{\mathrm{c}}$ rise.                                          |

| Stage 3:                                                                                                                                |

|                                                                                                                                         |

| <del></del> _                                                                                                                           |

| Stage 4:                                                                                                                                |

|                                                                                                                                         |

|                                                                                                                                         |

| Stage 5:                                                                                                                                |

|                                                                                                                                         |

|                                                                                                                                         |

|                                                                                                                                         |

(a)

(3)

- (b) Figure 2 shows the oscillator circuit after it has been modified by the addition of:

- two diodes  $D_1$  and  $D_2$

- a potential divider that has a total resistance value of  $(R_{\rm A}$  +  $R_{\rm B})$ .

Figure 2

In this particular circuit:

- the time  $t_{\rm H}$  for the output signal to be HIGH is given by  $t_{\rm H}$  = 0.7C (R +  $R_{\rm B}$ )

- the time  $t_{\rm L}$  for the output signal to be LOW is given by  $t_{\rm L}$  = 0.7C (R +  $R_{\rm A}$ ).

| State and explain the effect of this change on:       |                                   |

|-------------------------------------------------------|-----------------------------------|

| • the mark-to-space ratio ( $t_{ m H}$ : $t_{ m L}$ ) |                                   |

| • the pulse rate frequency (PRF).                     |                                   |

| mark-to-space ratio                                   |                                   |

|                                                       |                                   |

|                                                       |                                   |

|                                                       |                                   |

|                                                       |                                   |

|                                                       |                                   |

| DDE                                                   |                                   |

| PRF                                                   |                                   |

|                                                       |                                   |

|                                                       |                                   |

|                                                       |                                   |

|                                                       |                                   |

|                                                       |                                   |

| 77                                                    | (4)<br>Total 7 marks)             |

| т)                                                    | (4)<br><sup>-</sup> otal 7 marks) |

The slider of the potential divider is moved towards  $\boldsymbol{X}$ , as shown in **Figure 2**.

3.

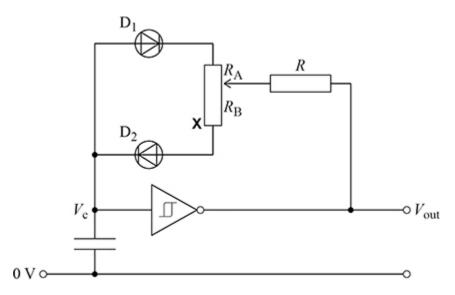

A burglar-alarm system in a house sounds an alarm during the hours of darkness when **one** of the following conditions is met:

- the door is opened

- the window is opened

- both the door and the window are opened.

**Figure 1** shows the main burglar-alarm subsystems and the logic status for the inputs and output.

(a) The table below is a partially completed truth table for the logic subsystem.

|   | Inputs |   | Output |

|---|--------|---|--------|

| С | В      | Α | Q      |

| 0 | 0      | 0 | 0      |

| 0 | 0      | 1 | 0      |

| 0 | 1      | 0 | 0      |

| 0 | 1      | 1 | 0      |

| 1 | 0      | 0 | 1      |

| 1 | 0      | 1 |        |

| 1 | 1      | 0 |        |

| 1 | 1      | 1 |        |

Complete the table above.

(1)

**Figure 2** shows the symbol of the push-to-make switch used in the door detector. When the door is closed, the switch button is pushed down onto the contacts. It automatically releases when the door opens.

Figure 2

(b) Complete **Figure 3** to show how this switch, together with a 10 k $\Omega$  resistor, can be connected to create the door detector circuit in **Figure 1**.

Label the output of the circuit with an X.

Figure 3

0 V O\_\_\_\_\_\_O

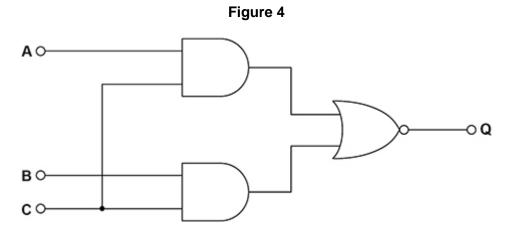

Figure 4 shows a logic circuit for a different alarm system.

(c) Write the Boolean algebra expression for **Q** in terms of inputs **A**, **B** and **C**. In your answer use only AND and NOR operators.

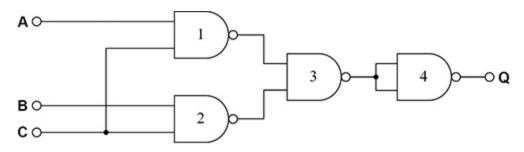

(d) **Figure 5** shows a logic circuit that has the same function as the circuit in **Figure 4**. Only one type of gate is used in the circuit in **Figure 5**.

Figure 5

State the logic function performed by gate 4.

\_\_\_\_

(1)

(e) Microchips containing two-input logic gates are mass-produced. Each microchip contains four identical logic gates.

A manufacturer of the logic circuit used in the burglar alarm chooses to make the circuit in **Figure 5** rather than that in **Figure 4**.

| Suggest | why. |

|---------|------|

|---------|------|

(1)

(Total 7 marks)

A Johnson decade counter uses a Johnson counter together with decoding logic. This arrangement produces a single logic 1 at a series of outputs Q<sub>0</sub>–Q<sub>9</sub> in a continuous sequence.

|                         | al difference and <b>one</b> functional similarity between how a Johns<br>BCD counter output their counts. |

|-------------------------|------------------------------------------------------------------------------------------------------------|

| functional difference   |                                                                                                            |

|                         |                                                                                                            |

|                         |                                                                                                            |

|                         |                                                                                                            |

| functional similarity _ |                                                                                                            |

|                         |                                                                                                            |

|                         |                                                                                                            |

|                         |                                                                                                            |

(a)

(2)

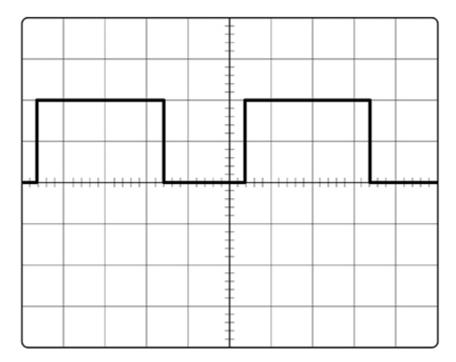

(b) An astable oscillator produces a continuous train of pulses.

The figure below shows the display of the pulses on an oscilloscope.

The oscilloscope settings are:

voltage gain = 2 V / division time-base = 50 µs / division.

Determine the duty cycle and frequency of the signal.

duty cycle = \_\_\_\_\_

frequency = \_\_\_\_\_kHz

(3)

(c) The astable is adjusted to produce a 600 Hz test signal.

This signal is applied to the clock input of the BCD counter and to the clock input of the Johnson decade counter.

The outputs of the BCD counter are  $Q_0$ ,  $Q_1$ ,  $Q_2$  and  $Q_3$  where  $Q_0$  is the least significant part of the output.

The outputs of the Johnson decade counter are  $Q_0, Q_1, Q_2 \dots Q_n$ .

Determine the frequency of the pulses available at  ${\sf Q}_2$  for each counter.

BCD counter: frequency of pulses = \_\_\_\_\_ Hz

Johnson decade counter: frequency of pulses = \_\_\_\_\_ Hz

(2) (Total 7 marks)

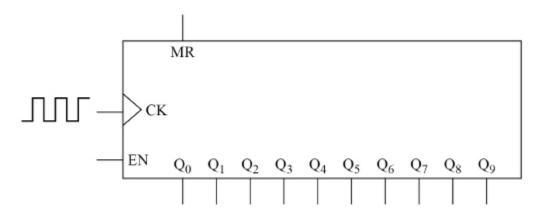

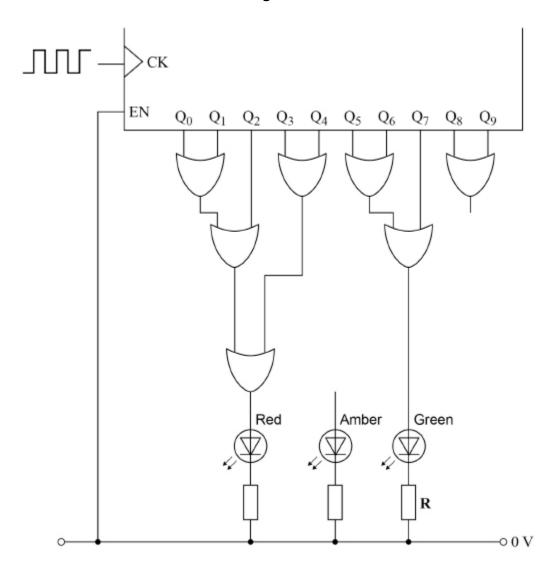

**5.** Figure 1 shows the basic layout for a Johnson decade counter. The main input is the clock (CK). The main outputs are shown as  $Q_0$  to  $Q_9$ .

Figure 1

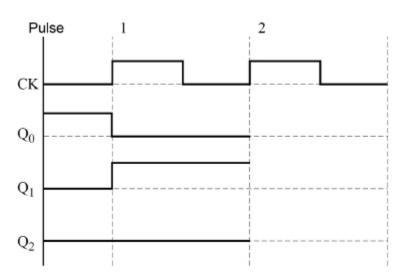

(a) Figure 2 shows part of the timing diagram for a Johnson decade counter.

This timing diagram shows the output logic states against time. The counter is reset to make  $Q_0 = 1$  and then the first two pulses are applied.

Complete **Figure 2** to show the logic states of  $Q_0$ ,  $Q_1$  and  $Q_2$ .

Figure 2

(2)

(b) A student sets up the counter to make the traffic light sequence:

$$\textbf{red} \rightarrow \textbf{red + amber} \rightarrow \textbf{green} \rightarrow \textbf{amber}$$

The sequence then repeats.

**Figure 3** shows a partially completed diagram for producing this sequence.

Draw an OR gate and connections on **Figure 3** so that the LEDs go through the complete sequence.

Figure 3

(1)

| 2 _ |                                                                                                                |

|-----|----------------------------------------------------------------------------------------------------------------|

|     | <del></del>                                                                                                    |

|     | potential difference across the green LED is 2.1 V when it is lit. The current through it uld not exceed 9 mA. |

| ogi | ogic gate outputs are:<br>c low = 0 V<br>c high = 9 V.                                                         |

|     | e student suggests that a resistor of resistance 720 $\Omega$ and a tolerance of ±5% should bed for ${f R}.$   |

| Ded | duce whether the student's suggestion would be suitable.                                                       |

|     |                                                                                                                |

|     |                                                                                                                |

|     |                                                                                                                |

|     |                                                                                                                |

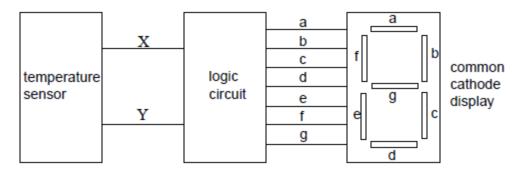

A fridge is fitted with a temperature-sensing unit to indicate whether the temperature inside the fridge is too high, too low, or at a safe temperature.

The system consists of a temperature sensor that produces a 2-bit binary output, a logic circuit and a low current, common cathode 7-segment display.

**Figure 1** shows a block diagram of the system.

6.

Figure 1

**Table 1** shows the operation of the system.

Table 1

| Fridge<br>temperature |   | erature<br>output | 7-segment<br>display |

|-----------------------|---|-------------------|----------------------|

|                       | X | Y                 | output               |

| < 3 °C                | 0 | 0                 | L                    |

| 3 °C to 4 °C          | 0 | 1                 | S                    |

| 4 °C to 5 °C          | 1 | 0                 | S                    |

| > 5 °C                | 1 | 1                 | Н                    |

(a) Complete **Table 2** to show the logic signals required on lines a to g to display the specified characters.

Table 2

| X | Y | а | b | С | d | e | f | g | Display |

|---|---|---|---|---|---|---|---|---|---------|

| 0 | 0 |   |   |   |   |   |   |   | L       |

| 0 | 1 |   |   |   |   |   |   |   | S       |

| 1 | 0 |   |   |   |   |   |   |   | S       |

| 1 | 1 |   |   |   |   |   |   |   | Н       |

|               |                                  |                                                                      | Figure                   | 2             |                      |        |   |

|---------------|----------------------------------|----------------------------------------------------------------------|--------------------------|---------------|----------------------|--------|---|

| a b c d e f g | method A  f  g  c  State one dis | common 0 sadvantage of                                               |                          | a b c d e f g | method B  f b  e g c | common | V |

| (ii)          | current in ea                    | e value of the c<br>ch segment to<br>voltage from th<br>the 7-segmen | 20 mA.<br>ne logic circu | it is 5 V and | ·                    |        |   |